## IBM T400 电路分析

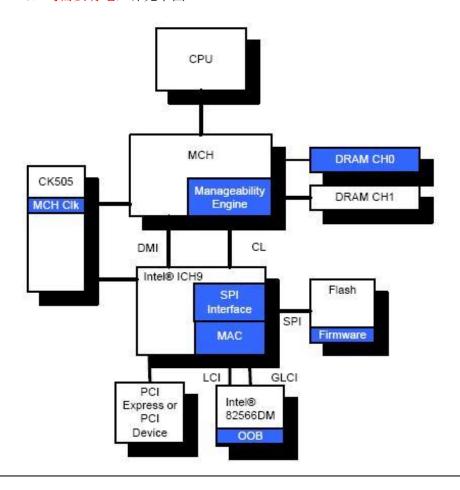

INTEL 芯片组从 965 开始,在 GMCH 与 ICH 中增加了 Managealibity engine(管理引擎即 ME 模块),GMCH 与 ICH 之间除了有 DMI 总线用于通讯,另增加了 C-LINK(控制总线)用于实现 INTE AMT 功能

INTEL AMT 其全称为 Intel Active Management Technology (英特尔主动管理技术),它实质上是一种集成在芯片组中的嵌入式程序,不依赖特定的操作系统,这也是 AMT 与远程控制软件最大的不同。该技术允许 IT 经理远程管理和修复联网的计算机系统,而且服务过程是对于服务对象完全透明的,从而节省了用户的时间和计算机维护成本。通俗讲就是当系统崩溃或主机蓝屏时,可以远程恢复/修复操作系统。AMT 技术支持的驱动器重定向(IDE Redirection)功能,可以将管理主机的驱动器资源通过网络虚拟至目标主机上,在目标主机一侧,其认为这就是它的本地资源。英特尔在 AMT 中内置了 KVM(Keyboard-Video-Mouse),可以看到问题主机的屏幕及操作鼠标和键盘。管理员可以在任何地方通过网络向服务器发出操作指令,完全现场级操作。AMT 中的 SOL/IDE-R(Serial-Over-LAN/IDE Redirection)使 IT 经理可以远程执行开关机,可以把光盘做成镜像后启动目标主机。由于其采用的网卡支持 OOB,即带外管理,英特尔 AMT 的有效性与操作系统及操作系统的网络连通状态无关(即在网卡无驱的情况下,AMT 功能照样实现网络通讯)

从硬件上讲,INTEL 965 以上的芯片组,如 965PM/GM 、GM/PM45 、HM55 、HM65 均可完美支持。除芯片组需支持 AMT 以外,AMT 本身的嵌入式系统程序,其与主板 BIOS 通常存储在一个芯片中。

支持 AMT 的系统在 **S5** 休眠状态时,C-LINK 部分、时钟芯片、INTEL PHY LAN、SPI BIOS、MEMORY(CHANNELO DIMMO)均需要有电,详见下图

INTEL 芯片组从 ICH8M 开始,ACPI 中休眠逻辑控制信号增加了一个 SLP M#。

| SLP_M# | О | Manageability Sleep State Control: This signal is used to control power planes to the Intel AMT sub-system. IF no ME firmware is present, SLP_M# will have the same timings as SLP_S3#. |

|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

SLP\_M#: 此信号用于控制 INTEL AMT 子系统的电源。当 ME 固件不存在时,SLP\_M#与 SLP\_S3#同时产生/关闭(时序步骤一致)。

重新定义了 SLP\_S4#的功能

| Name             | Туре | Description                                                                                                                                                                                                                                                                                                                         |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |      | <b>S4 Sleep Control</b> : SLP_S4# is for power plane control. This signal shuts power to all non-critical systems when in the S4 (Suspend to Disk) or S5 (Soft Off) state.                                                                                                                                                          |

| <b>SLP_S4#</b> 0 |      | NOTE: This pin must be used to control the DRAM power in order to use the ICH8's DRAM power-cycling feature. Refer to Chapter 5.13.11.2 for details                                                                                                                                                                                 |

|                  |      | NOTE: In a system with Intel AMT support, this signal should be used to control the DRAM power. In M1 state (where the host platform is in S3-S5 states and the manageability sub-system is running) the signal is forced high along with SLP_M# in order to properly maintain power to the DIMM used for manageability sub-system. |

SLP\_S4#: 当系统处于 S4、S5 休眠状态,用于控制其所控制的电压的开关。备注: 当系统打开 AMT 功能时,用于控制内存电压的开关。在 M1 状态(当主平台处于 S3-S5 状态且 ME 子系统运行时)SLP\_S4#被 SLP\_M#强制拉高,用于系统在 AMT 状态下时开启内存电压。

AMT 功能打开时,各 SLP\_SX#信号逻辑如下

| 24/1944 1 |    |    |    |    |  |  |  |

|-----------|----|----|----|----|--|--|--|

| 信号        | S0 | S3 | S4 | S5 |  |  |  |

| SLP_S3#   | 1  | 0  | 0  | 0  |  |  |  |

| SLP_S4#   | 1  | 1  | 1  | 1  |  |  |  |

| SLP_S5#   | 1  | 1  | 1  | 0  |  |  |  |

| S4_STATE# | 1  | 1  | 0  | 0  |  |  |  |

| SLP_M#    | 1  | 1  | 1  | 1  |  |  |  |

当 AMT 功能打开,系统处于 S5 休眠状态时,SLP\_S4#用于控制内存电压的保留,SLP\_M#用于控制时钟芯片、C-LINK 部分、INTEL PHY LAN、SPI BIOS 等电压的保留。

IBM T400 采用的是 PM45 芯片组, 南桥为 ICH9ME(82801IEM, 只有增强有 ICH 才支持 AMT 功能)。支持 AMT 功能, 在 CMOS 设置中可以打开或屏蔽 AMT 功能。

T400 保护隔离与电池充放电电路同 T60 原理一致,原理请大家参阅本人另一文章: IBM T6 电路分析。本文分析的 T400 时序均为 AMT 功能打开时

## 一、T400 待机时序分析

- 1. TB62506 输出 VCC3SW 给 PMH7 作为待机电压, PMH7 内部震荡器工作从 26 脚输出方波, 从 25 脚返回锯齿波, 作为 PMH7 的待机时钟, VCC3SW 其中一路过电阻 R309 经电容 C304 延时加至 PMH7 的 SWPWRG 作为 PMH7 的复位。

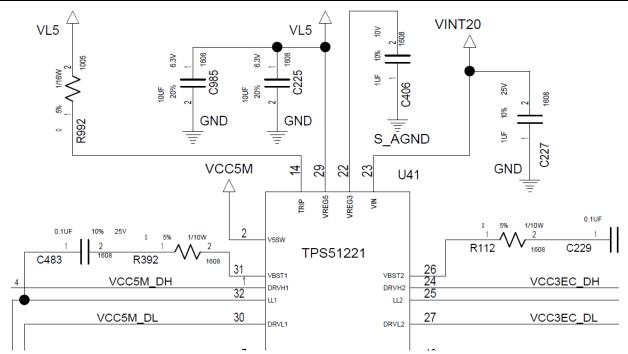

- 2. VINT20 供至 TPS51221 的 VIN 脚,在芯片 12 脚 EN 脚有 3.3V 开启信号后,芯片 29 脚 VREG5 输出 5V 线性电压 VL5.

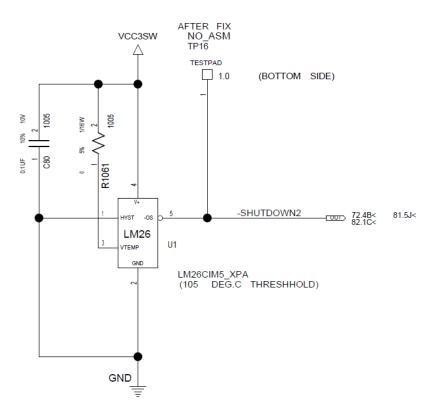

此处 TPS51221 的 EN 信号由 SHUTDOWN2#及 PWRSHUTDOWN#逻辑相与而来 其中 PWRSHUTDOWN#来自于 BD4176KVT(TB62513) SHUTDOWN2 来自 CPU 温控电路 U1

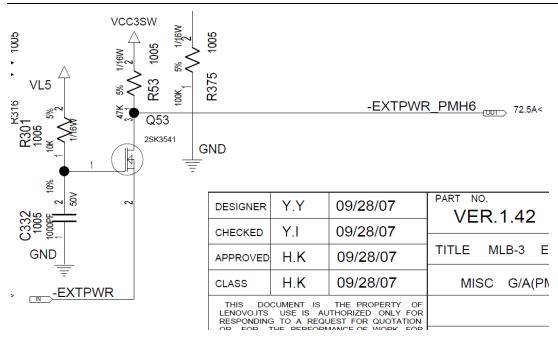

3. 适配器插入检测信号 EXTPWR#为有效电位低电位,TPS51221 产生的 5V 线性电压 VL 加至 Q53 的 G 极,Q53 导通(2SK3019 门坎电压 2.5V),产生 EXTPWR\_PMH6#至 PMH7 的 EXTPWR#脚,告知 PMH7 此时适配器已插入,作为其发出 M 路电路开启信号的前提。

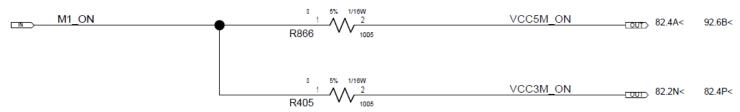

4.PMH7 收到 EXTPWR#适配器插入检测信号、高电平的 SHUTDOWN2#后,发出 M1\_ON。M1\_ON 过电阻 R866 更名为 VCC5M\_ON、过电阻 R405 更名为 VCC3M\_ON

VCC5M\_ON、VCC3M\_ON 至待机芯片 TPS51221 的 EN1、EN2 脚,开启 VCC3M VCC5M 待机电压 5、VCC3M 供至 ICH9ME 的 VCCSUS3\_3,VCC5M 供至 ICH9ME 的 V5REF\_SUS,作为 ICH9ME 的待机电压。 VCC3M、VCC5M、VCC5M\_ON 在 BD4176KVT 内存逻辑相与产生 MPWRG。MPWRG 加至 ICH9ME 的 RSMRST#脚位,通知 ICH9ME 此时待机电压电源好。

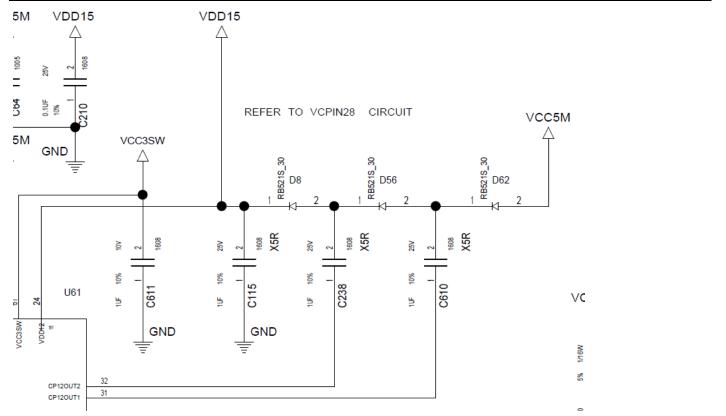

BD4176KVT 在 VCC3SW 电压稳定,MPWRG 信号为高后,从 CP12OUT、CP12OUT2 输出脉冲方波,与 VCC5M 自举升 压产生 VDD15 的 15V 待机电压。

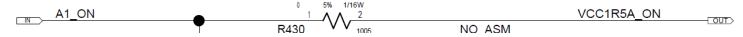

6. VCC3M 电压供至 BIOS 芯片,**AMT 功能打开时**,由 BIOS 配置 ICH9ME 的 SLP\_M#、SLP\_S4#的逻辑为高 ICH9M 输出高电平的 ICH\_SLP\_S4#至 PMH7,PMH7 发出 A1\_ON。A1\_ON 过电阻 R430 更名为 VCC1R5A\_ON

VCC1R5A\_ON 至 MAX1540 的 ON2 脚,开启 VCC1R5A 的内存主电压。VCC1R5A 电压稳定后,MAX1540 产生 APWRG。

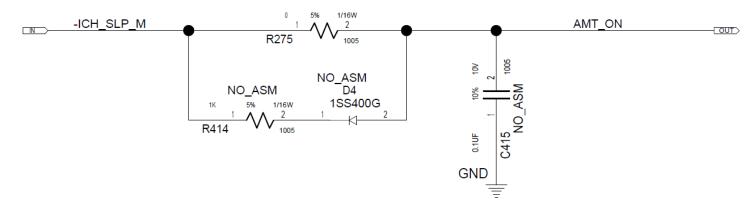

7. ICH9M 输出高电平的 ICH\_SLP\_M#, ICH\_SLP\_M#过电阻 R275 更名为 AMT\_ON。

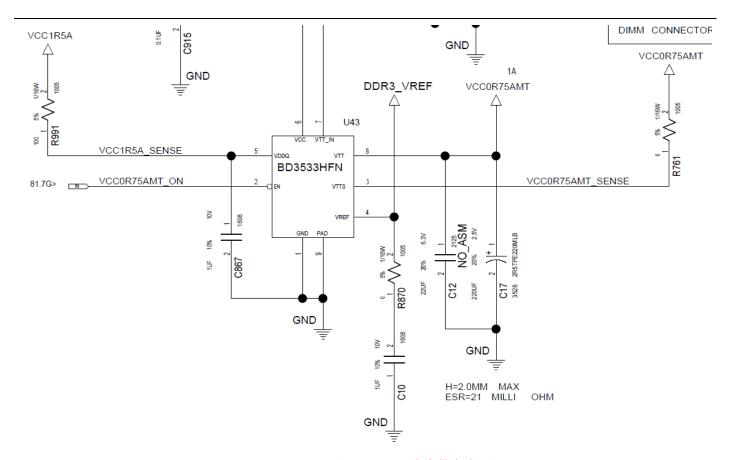

AMT\_ON 过电阻 R1075 更名为 VCCOR75AMT\_ON,VCCOR75AMT\_ON 至 BD3533 开启 VCCOR75AMT,作为内存 VTT 电压。开启 DDR3\_VREF,作为内存参考电压。

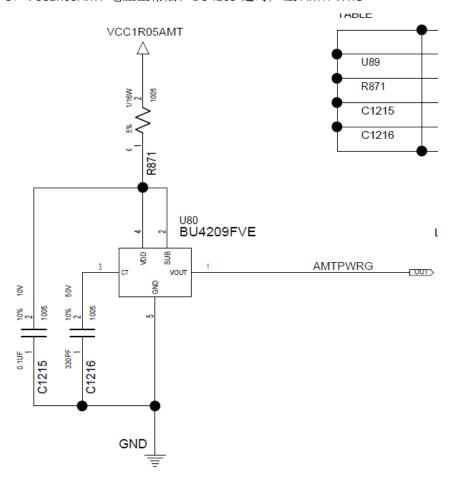

AMT\_ON 至 MAX1540 的 ON1 脚,开启 VCC1R05AMT,作为 C\_LINK 总线供电电压。VCC1R05AMT 电压正常后,MAX1540 产生 1R05AMT\_PWRG。

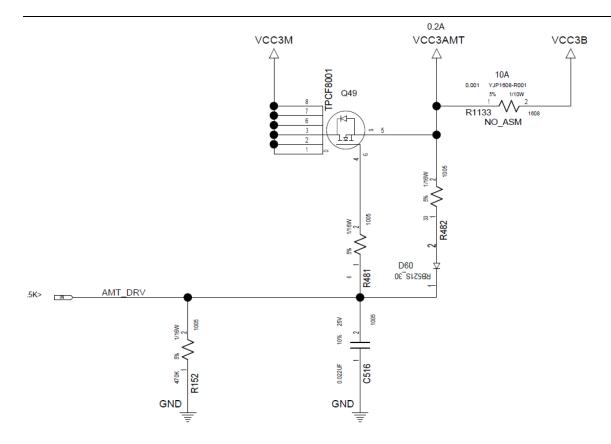

AMT\_ON 至 BD4176KVT 的 RD4\_ON, BD4176KVT 输出升压成 15V 的 AMT\_DRV 至 Q49, 将 VCC3M 电压转换成 VCC3AMT, 作为**时钟芯片的主供电**

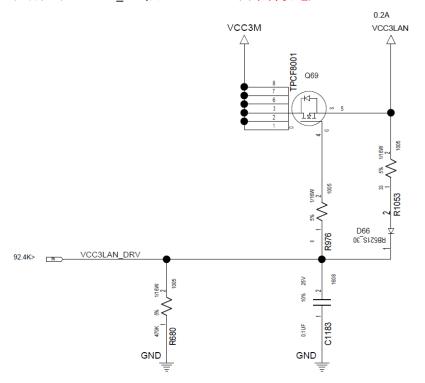

AMT\_ON 经或门电路 U79 产生 VCCLAN\_ON。VCCLAN\_ON 至 BD4176KVT 的 RD6\_ON,BD4176KVT 输出升压成 15V 的 驱动信号 VCCLAN\_DRV,开启 VCC3LAN 网卡特机电压。

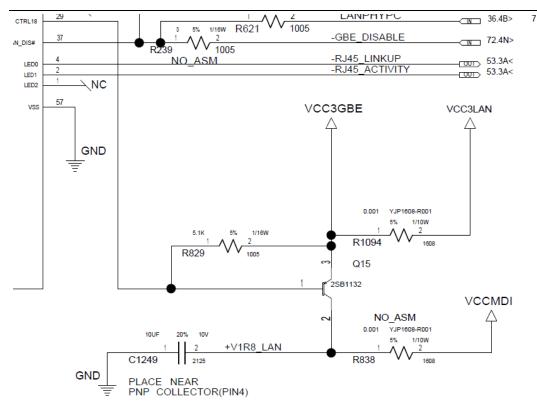

VCC3LAN 供至网卡,网卡发出 CRTL18,驱动 Q15 产生 VCC1R8AUX 网卡待机电压。

## 8. VCC1R05AMT 电压正常后, BU4209 延时产生 AMTPWRG

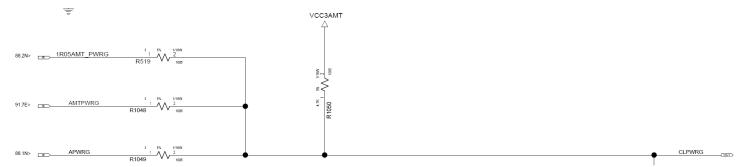

9. APWRG、1R05AMT\_PWRG、AMTPWRG 共同逻辑相与产生 CLPWRG 至 ICH9ME 的 CLPWROK,至此待机条件完全满足。

10. AMT 功能未打开时,ICH\_SLP\_S4#、ICH\_SLP\_M#均为低电平,其所控制的电压均在待机时不产生,因此待机时电压只有 VCC3M、VCC5M、VCC3LAN、VCC1R8AUX,谨记谨记!

## 二、T400 上电时序分析

- 1、按下电源,产生开机触发 PWRSWITCH#,一路直接加至 PMH7 的 32 脚,通知 PMH7 此时用户按下电源键一路转换为 PWRSW#加至 H8S,H8S 发出 PWRSW H8#至 ICH9ME 的 PWRBTN#脚位。

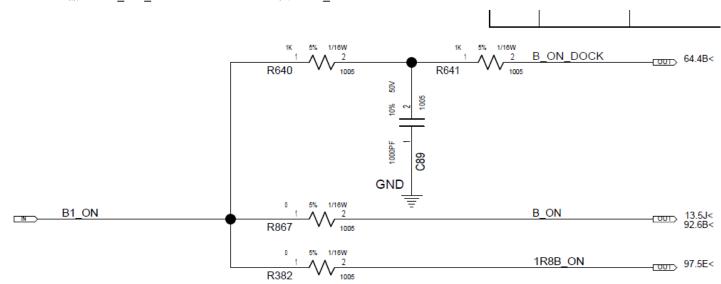

- 2、ICH9ME 输出 ICH\_SLP\_S3#至 PMH7,PMH7 发出 B1\_ON。

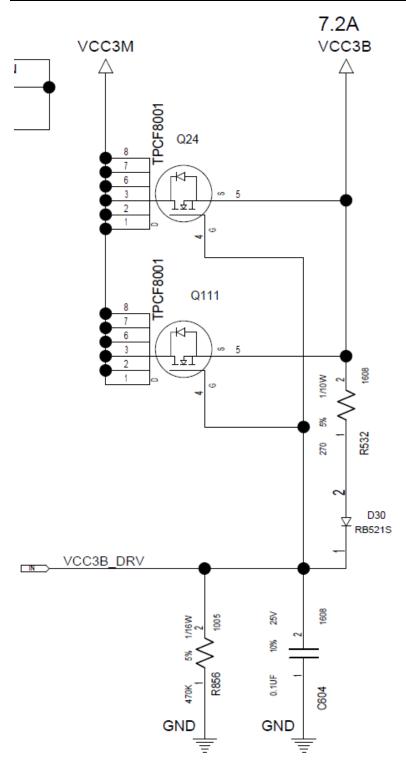

B1\_ON 过电阻 R867 更名为 B\_ON, 至 BD4176KVT 的 3B\_ON、5B\_ON、RD2\_ON, BD4176KVT 发出 15V 的 VCC3B\_DRV、VCC5B\_DRV、B\_DRV。

VCC3B\_DRV 驱动 Q24 将 VCC3M 转换成 VCC3B。

VCC5B\_DRV 驱动 Q23 将 VCC5M 转换成 VCC5B。

B\_DRV 驱动 Q11 将 VCC1R5A 转换成 VCC1R5B,同时驱动 Q120 将 VCC1R05AMT 转换成 VCC1R05B。

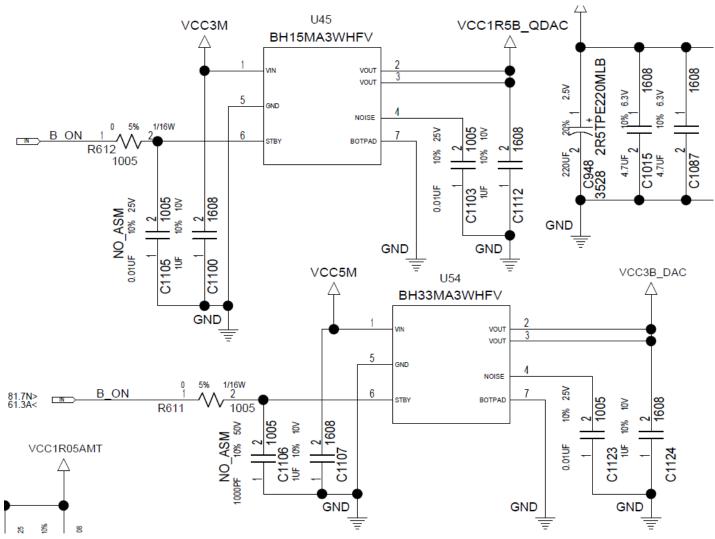

B\_ON 至 BH33MA(U54)将 VCC5M 降压成 VCC3B\_DAC,作为 GMCH 的 CRT 模块供电。 B\_ON 至 BH15MA(U45)将 VCC3M 降压成 VCC1R5B\_QDAC,作为 GMCH 的 TV 模块供电。

T400 是可以支持双显卡切换的,因此 GMCH 内置 CRT 模块、TV 模块、LVDS 模块均需有单独供电!!

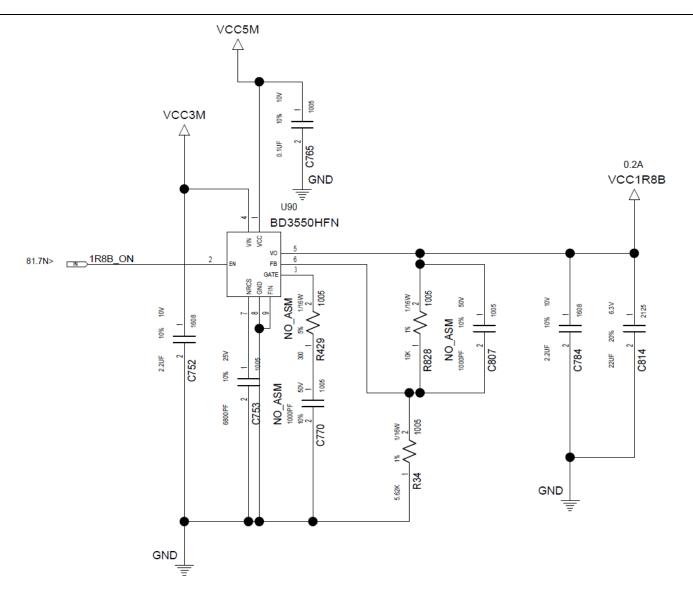

B1\_ON 过 R382 更名为 VCC1R8B\_ON, VCC1R8B\_ON 至 BD3550 (U90) 开启 VCC1R8B, 作为 GMCH 的 LVDS 模块供电。

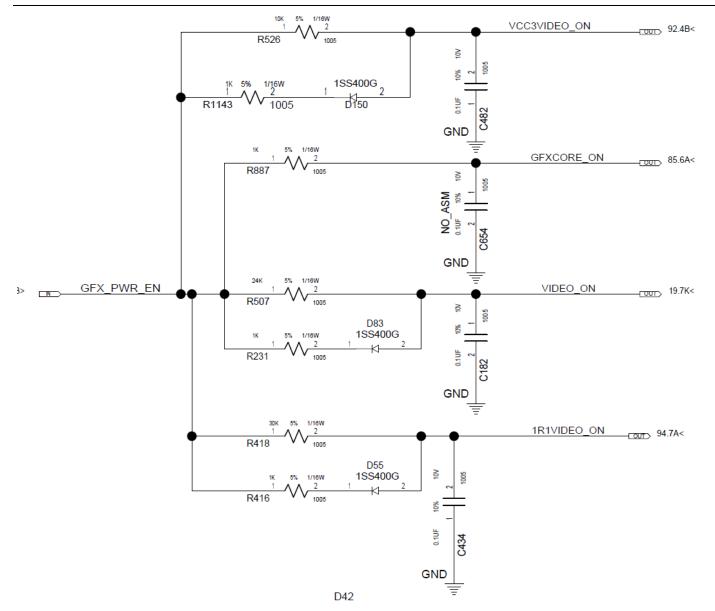

3. 当用户在 BIOS 设置中如果选择打开独立显卡(或是系统中切换成独立显卡时),此时 ICH9ME 的 GPIO49 发出 GFX\_PWR\_EN。

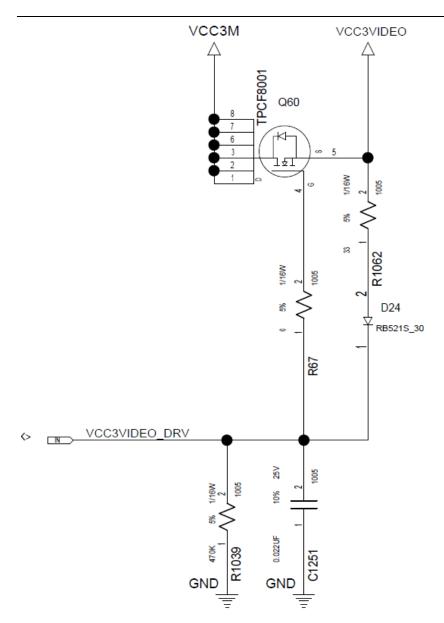

GFX\_PWR\_EN 过电阻 R526 更名为 VCC3VIDEO\_ON。VCC3VIDEO\_ON 至 BD4176KVT 的 RD5\_ON,BD4176KVT 输出 15V 的 VCC3VIDEO\_DRV。驱动 Q60 将 VCC3M 转换成 VCC3VIDEO。

GFX\_PWR\_EN 过电阻 R507 更名为 VIDEO\_ON。

VIDEO\_ON 至 VT351(u66)开启 VCC1R8VIDEO。

VIDEO\_ON 至 BD3550 开启 VCC1R8VIDEO\_PLL。

GFX\_PWR\_EN 过电阻 R418 更名为 1R1VIDEO\_ON。

1R1VIDEO\_ON 至 BD3508 开启 VCC1R1VIDEO。

GFX\_PWR\_EN 过电阻 R887 更名为 GFXCORE\_ON, GFXCORE\_ON 至 ADP3209 的 EN 脚, 开启显卡核心电压 VCCGFXCORE。当 VCCFGXCORE 电压稳定后,ADP3209 输出 DGFX\_PWRGD 至 ICH9ME,ICH9ME 发出独立显卡的开启信号 DISCRETE ENABLE,用于切换独显的 LVDS、VGA、TV 等信号通道。

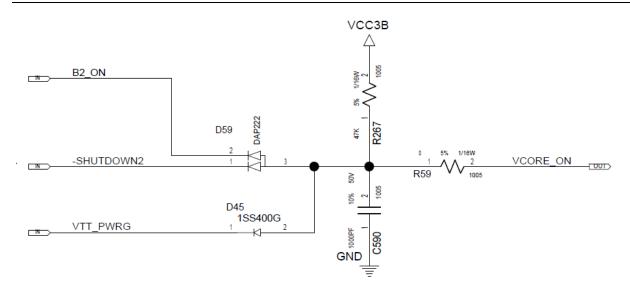

**4.** PMH7 发出 B1\_ON 后,延时产知 B2\_ON。B2\_ON 与 SHUTDOWN2、VTT\_PWRG 逻辑相与产生 CPU 核心电压开启信号 VCORE\_ON

VCORE\_ON 至 ADP3207 的 EN 脚,开启 CPU 核心电压 VCCCPUCORE。当 VCCCPUCORE 电压稳定后,ADP3207 发出 VR PWRGD。

- 5. VR\_PWRGD 信号发至 ICH9ME 的 VRMPWRGD 脚,在 ICH9ME 内部,VRMPWRGD 与 SLP\_S3#逻辑相与,产生时钟 开启认号 CK\_PWRGD,开启时钟信号。

- 6. BD4176KVT 在检测其所切换的各路电压(M 路电压、A 路电压、B 路电压)均正常的情况下,发出 BPWRG。

Truth Table

| 5M_ON | 3M_ON | 5B_ON | 3B_ON | APGS | VCC5B                                                              | VCC3B                                                     | B_PGS |

|-------|-------|-------|-------|------|--------------------------------------------------------------------|-----------------------------------------------------------|-------|

| L     |       |       |       |      |                                                                    |                                                           | L     |

|       | L     |       |       |      |                                                                    |                                                           | L     |

|       |       | ١     |       |      |                                                                    |                                                           | L     |

|       |       |       | L     |      |                                                                    |                                                           | L     |

|       |       |       |       | L    |                                                                    |                                                           | L     |

|       |       |       |       |      | VCC5B <detection td="" voltage<=""><td></td><td>L</td></detection> |                                                           | L     |

|       |       | ·     |       |      |                                                                    | VCC3B <detection td="" voltage<=""><td>L</td></detection> | L     |

| Н     | Н     | ·     | Н     | Ι    | VCC5B>Recovery Voltage                                             | VCC3B>Recovery Voltage                                    | Н     |

7. BPWRG 加至 GMCH,作为 GMCH 的工作条件。BPWRG 至 ICH9ME 中的 PWROK。通知 ICH9ME 此时系统电压电源好。

8.在 ICH9ME 内部,VRMPWRGD 与 PWROK 两信号逻辑相与产生 CPUPWRGD,发至 CPU。缓冲输出 PLTRST#。PLTRST#加至 GMCH。在 GMCH 的各电压、时钟、PWROK、PLTRST#均正常的情况下,北桥发出 CPURST#至 CPU。

2012/4/4 04:13

迅维网培训中心 笔记本讲师 陈红喜(双喜) 原创 QQ: 157649191 2434401547 电话: 0755-61506416 15/15